**CHUKA**

#### **UNIVERSITY**

#### **UNIVERSITY EXAMINATIONS**

#### **RESIT/SPECIAL EXAMINATION**

# THIRD YEAR EXAMINATION FOR THE AWARD OF DEGREE OF BACHELOR OF COMPUTER SCIENCE

COSC 312: COMPONENTS AND DESIGN TECHNIQUES FOR DIGITAL SYSTEMS

STREAMS: BSC TIME: 2 HOURS

DAY/DATE: WEDNESDAY 03/02/2021 5.00 P.M - 7.00 P.M.

#### **INSTRUCTIONS**

- Answer all questions in section A and any other two questions from section B.

- No Reference Material is allowed in the exam Room.

- All Mobile phones should be switched off in the exam room.

- Use diagrams where possible to illustrate your answer

#### **SECTION A (COMPULSORY)**

## **QUESTION 1(COMPULSORY) [30 MARKS]**

- a) With the help of a diagram, differentiate between Mealy and Moore machine

- (4 marks)

- b) Explain the four basic movement of data through a shift register (4 marks)

- c) Using "ieee.std\_logic\_1164.all" library, write a VHDL code of a 4 bit counter. (5 marks)

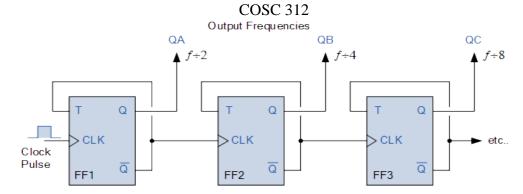

- d) Below is a diagram of a divide by x (where x=2, 4 and 8), use it to answer the questions below.

i) Explain how the above flip flop circuit works

(3 marks)

ii) Write the truth table of the above circuit in d(i) above

(3 marks)

e) Below is a truth table for the conversion of binary number to Gray code. Use it to answer the questions below.

| Binary           |                       |                       | Gray code                              |                                               |                                               |                                                                     |                                                       |

|------------------|-----------------------|-----------------------|----------------------------------------|-----------------------------------------------|-----------------------------------------------|---------------------------------------------------------------------|-------------------------------------------------------|

| $\boldsymbol{b}$ | c                     |                       | X                                      |                                               | y                                             | z                                                                   |                                                       |

| 0                | 0                     |                       | 0                                      |                                               | 0                                             | 0                                                                   | _                                                     |

| 0                | 1                     |                       | 0                                      |                                               | 0                                             | 1                                                                   |                                                       |

| 1                | 0                     |                       | 0                                      |                                               | 1                                             | 1                                                                   |                                                       |

| 1                | 1                     |                       | 0                                      |                                               | 1                                             | 0                                                                   |                                                       |

| 0                | 0                     |                       | 1                                      |                                               | 1                                             | 0                                                                   |                                                       |

| 0                | 1                     |                       | 1                                      |                                               | 1                                             | 1                                                                   |                                                       |

| 1                | 0                     |                       | 1                                      |                                               | 0                                             | 1                                                                   |                                                       |

| 1                | 1                     |                       | 1                                      |                                               | 0                                             | 0                                                                   |                                                       |

|                  | 0<br>0<br>1<br>1<br>0 | b c 0 0 0 1 1 1 0 0 0 | b c<br>0 0<br>0 1<br>1 0<br>1 1<br>0 0 | b c x   0 0 0   0 1 0   1 0 0   1 1 0   0 0 1 | b c x   0 0 0   0 1 0   1 0 0   1 1 0   0 0 1 | b c x y   0 0 0 0   0 1 0 0   1 0 0 1   1 1 0 1   0 0 1 1   0 1 1 1 | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

i) Write the un-minimized SOP logic circuit equations that converts binary to Gray code (3 marks)

ii) Minimize the equations above

(6 marks)

iii) Draw the minimized SOP single circuit of binary to gray code

(2 marks)

# **SECTION B** (Answer **two question** from this section)

# **QUESTION 2 [20 MARKS]**

- a) A certain digital device could count number 1 up to 8 in binary numbers. Draw a POS circuit which will enable this to device give output of logic 1, only where there are two consecutive ones. i.e. 011, 110 etc. (5 marks)

- b) Use Boolean algebra laws to prove that the following circuits are the same

i)

$$(A + B)(A+C) = AC + \overline{A}B$$

(4 marks)

ii)

$$A + \overline{A}B = A$$

(3 marks)

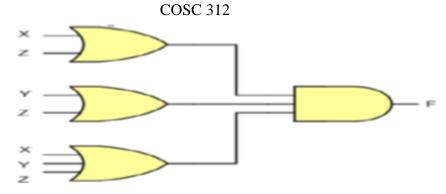

c) Below is a circuit implemented using OR gates and AND gates, use it to answer the questions below.

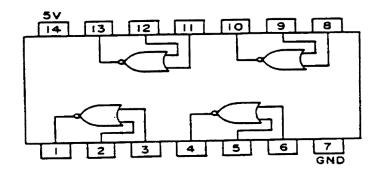

- i) Convert the above circuit to use NOR gates only (4marks)

- ii) Show the circuit diagram showing the implementation of the above circuit using the 7400 series NOR gate IC below (4marks)

## **QUESTION 3 [20 MARKS]**

- a) With reference to digital comparator (that compares 2-inputs A and B, then gives 3-outputs C, D and E).

- i) Draw the truth table of the comparator, such that: if A<B then only C is logic high, else if A=B then only D is logic high, otherwise if A>B then only E is logic high (4 marks)

- ii) Draw a circuit diagram of the above comparator( show workings) (6 marks)

- b) Using a TTL diagram, explain the operation of a NOR gate. (4 marks)

- c) With the help of a circuit diagram, explain how a 4 to 1 multiplexer work (6 marks)

## **QUESTION 4 [20 MARKS]**

- a) With the help of a diagram, explain how a decimal to 4bit binary coded decimal encoder functions (7 marks)

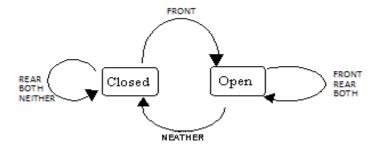

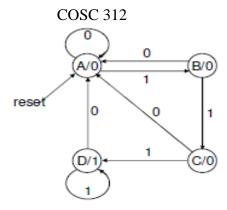

- b) Below is a FSM (finite state machine), use it to answer the questions below

- i) Write the state transition table (4 marks)

- ii) Use K-map to minimize the outputs (5 marks)

- iii) Draw the circuit of the minimized output (4 marks)

## **QUESTION 5 [20 MARKS]**

a) Use the following circuit to answer the questions below

$$G = (A+B)(A+C) + AB$$

- i) Perform a K-Map SOP minimization of the above logic equation (4 marks)

- ii) Perform a K-Map POS minimization of the above logic equation (3 marks)

- b) With reference to digital substractor (let it incorporate the borrow or opposite of carry)

- i) Using a truth table, explain the operation of a substractor (4 marks)

- ii) Draw the circuit diagram of the substractor (show minimizations) (6 marks)

- c) Below is a simple door open and lock FSM, explain how it functions (3 marks)